安定時間

外觀

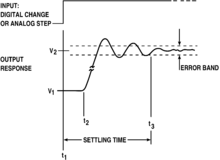

安定時間(Settling time)也稱為整定時間,是指放大器或控制系統在步階輸入後,輸出到達最終值,且其誤差可維持在一定範圍(一般是會對稱於最終值)內的時間,是暫態響應的特性之一。安定時間包括很短的傳播延遲,加上輸出依照瞬態率振盪到最終值附近的時間,以及最後安定在允許誤差附近的時間。

有能量儲存的系統無法立即反應,當輸入變化或有擾動時會有暫態的現象[1]。

定義

[編輯]Tay, Mareels and Moore(1997)定義安定時間為「輸出到達最終值附近,且和最終值之間的誤差維持在一定範圍(一般是5%到2%)內所需要的時間。」[2]

數學細節

[編輯]安定時間和系統響應及時間常數有關。

一階系統

[編輯]

一階系統較少定義安定時間,但一階系統在三倍時間常數後,其輸出和穩態的誤差降至,五倍時間常數後,其輸出和穩態的誤差降至[3],一般已可以忽略其誤差[4]。

二階系統

[編輯]若二階欠阻尼系統的阻尼比,其步階響應下的安定時間可以用以下式來近似:

因此,誤差在2%內的安定時間為:

參考資料

[編輯]- ^ Modern Control Engineering (5th Edition), Katsuhiko Ogata

- ^ Tay, Teng-Tiow; Iven Mareels; John B. Moore. High performance control. Birkhäuser. 1997: 93. ISBN 0-8176-4004-5.

- ^ 电工技术. 清華大學出版社有限公司. 2001: 98–. ISBN 978-7-302-04927-2.

- ^ 電路學(上). 五南圖書出版股份有限公司. : 251–. ISBN 978-957-11-4162-6.

- ^ Richard C. Dorf; Robert H. Bishop. Modern Control Systems. Addison Wesley. 1995: 223. ISBN 0-201-50174-0.

相關條目

[編輯]外部連結

[編輯]- Second-Order System Example

- Op Amp Settling Time (頁面存檔備份,存於互聯網檔案館)

- Graphical tutorial of Settling time and Risetime

- MATLAB function (頁面存檔備份,存於互聯網檔案館) for computing settling time, rise time, and other step response characteristics