金屬氧化物半導體場效電晶體

此條目需要补充更多来源。 (2015年9月9日) |

金屬氧化物半導體場效電晶體(簡稱:金氧半場效電晶體;英語:Metal-Oxide-Semiconductor Field-Effect Transistor,縮寫:MOSFET),是一種可以廣泛使用在模拟電路與数字電路的場效電晶體。金屬氧化物半導體場效電晶體依照其通道極性的不同,可分為电子占多数的N通道型與空穴占多数的P通道型,通常被稱為N型金氧半場效電晶體(NMOSFET)與P型金氧半場效電晶體(PMOSFET)。

以金氧半場效電晶體(MOSFET)的命名來看,事實上會讓人得到錯誤的印象。因為MOSFET跟英文單字「metal(金屬)」的第一個字母M,在當下大部分同類的元件裡是不存在的。早期金氧半場效電晶體閘極使用金屬作為材料,但由於多晶矽在製造工藝中更耐高溫等特點,許多金氧半場效電晶體閘極採用後者而非前者金屬。然而,隨著半導體特徵尺寸的不斷縮小,金屬作為閘極材料最近又再次得到了研究人員的注意。

金氧半場效電晶體在概念上屬於絕緣閘極場效電晶體(Insulated-Gate Field Effect Transistor, IGFET)。而絕緣閘極場效電晶體的閘極絕緣層,有可能是其他物質,而非金氧半場效電晶體使用的氧化層。有些人在提到擁有多晶矽閘極的場效電晶體元件時比較喜歡用IGFET,但是這些IGFET多半指的是金氧半場效電晶體。

金氧半場效電晶體裡的氧化層位於其通道上方,依照其操作電壓的不同,這層氧化物的厚度僅有數十至數百埃(Å)不等,通常材料是二氧化硅(SiO2),不過有些新的進階製程已經可以使用如氮氧化硅(silicon oxynitride, SiON)做為氧化層之用。

今日半導體元件的材料通常以矽為首選,但是也有些半導體公司發展出使用其他半導體材料的製程,當中最著名的例如國際商業機器股份有限公司使用硅與鍺的混合物所發展的矽鍺製程(SiGe process)。而可惜的是很多擁有良好電性的半導體材料,如砷化鎵(GaAs),因為無法在表面長出品質夠好的氧化層,所以無法用來製造金氧半場效電晶體元件。

當一個夠大的電位差施於金氧半場效電晶體的閘極與源極之間時,電場會在氧化層下方的半導體表面形成感應電荷,而這時就會形成反轉通道(inversion channel)。通道的極性與其汲極(drain)與源極相同,假設汲極和源極是n型,那麼通道也會是n型。通道形成後,金氧半場效電晶體即可讓電流通過,而依據施於閘極的電壓值不同,可由金氧半場效電晶體的通道流過的電流大小亦會受其控制而改變。

電路符號

[编辑]常用於金氧半場效電晶體的電路符號有多種形式,最常見的設計是以一條垂直線代表通道(Channel),兩條和通道平行的接線代表源極(Source)與汲極(Drain),左方和通道垂直的接線代表閘極(Gate),如下圖所示。有時也會將代表通道的直線以虛線代替,以區分增强型(enhancement mode,又稱增强式)金氧半場效電晶體或是耗尽型(depletion mode,又稱空乏式)金氧半場效電晶體。

由於集成電路晶片上的金氧半場效電晶體為四端元件,所以除了源極(S)、汲極(D)、閘極(G)外,尚有一基極(Bulk或是Body)。金氧半場效電晶體電路符號中,從通道往右延伸的箭號方向則可表示此元件為n型或是p型的金氧半場效電晶體。箭頭方向永遠從P端指向N端,所以箭頭從通道指向基極端的為p型的金氧半場效電晶體,或簡稱PMOS(代表此元件的通道為p型);反之則代表基極為p型,而通道為n型,此元件為n型的金氧半場效電晶體,簡稱NMOS。在一般分散式金氧半場效電晶體元件中,通常把基極和源極接在一起,故分散式金氧半場效電晶體通常為三端元件。而在積體電路中的金氧半場效電晶體通常因為使用同一個基極(common bulk),所以不標示出基極的極性,而在PMOS的閘極端多加一個圓圈以示區別。

幾種常見的MOSFET電路符號,加上接面場效電晶體一起比較:

|

|

|

|

|

P沟道 |

|

|

|

|

|

N沟道 |

| JFET | 增强型MOSFET | 增强型MOSFET(省略基極) | 空乏型MOSFET | ||

上圖中的金氧半場效電晶體符號中,基極端和源極端均接在一起,一般分立元件的MOSFET幾乎均如此,但在積體電路中的金氧半場效電晶體則並不一定是這樣連接。通常一顆積體電路晶片中相同通道的金氧半場效電晶體都共享同一個基極,故某些情況下的金氧半場效電晶體可能會使得源極和基極並非直接連在一起,例如串疊式電流源(cascode current source)電路中的部份NMOS就是如此。基極與源極沒有直接相連的金氧半場效電晶體會出現基板效應(body effect)而部份改變其操作特性,將在後面的章節中詳述。

金氧半場效電晶體的操作原理

[编辑]金氧半場效電晶體的核心

[编辑]

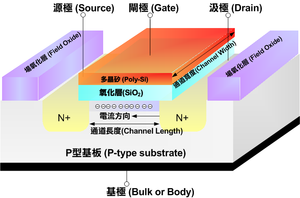

金氧半場效電晶體在結構上以一個金屬—氧化物層—半導體的電容為核心(現在的金氧半場效電晶體多半以多晶矽取代金屬作為其閘極材料),氧化層的材料多半是二氧化矽,其下是作為基極的矽,而其上則是作為閘極的多晶矽。這樣的結構正好等於一個電容器,氧化層為電容器中介電質,而電容值由氧化層的厚度與二氧化矽的介電係數來決定。閘極多晶矽與基極的矽則成為MOS電容的兩個端點。

當一個電壓施加在MOS電容的兩端時,半導體的電荷分佈也會跟著改變。

累积

[编辑]考慮一個p型的半導體(電洞濃度為NA)形成的MOS電容,当给电容器加负电压时,电荷增加(如C-V曲线左侧所示)。

耗尽

[编辑]相反,當一個正的電壓VGD施加在閘極與基極端(如圖)時,電洞的濃度會減少(称为耗尽,如C-V曲线中间所示),電子的濃度會增加。

反型

[编辑]當VGS夠強時,接近閘極端的電子濃度會超過電洞。這個在p-type半導體中,電子濃度(帶負電荷)超過電洞(帶正電荷)濃度的區域,便是所謂的反轉層(inversion layer),如C-V曲线右侧所示。

MOS電容的特性決定了金氧半場效電晶體的操作特性,但是一個完整的金氧半場效電晶體結構還需要一個提供多數載子(majority carrier)的源極以及接受這些多數載子的汲極。

金氧半場效電晶體的結構

[编辑]

左圖是一個n-type金氧半場效電晶體(以下簡稱NMOS)的截面圖。如前所述,金氧半場效電晶體的核心是位於中央的MOS電容,而左右兩側則是它的源極與汲極。源極與汲極的特性必須同為n-type(即NMOS)或是同為p-type(即PMOS)。左圖NMOS的源極與汲極上標示的「N+」代表著兩個意義:(1)N代表摻雜(doped)在源極與汲極區域的雜質極性為N;(2)「+」代表這個區域為高摻雜濃度區域(heavily doped region),也就是此區的電子濃度遠高於其他區域。在源極與汲極之間被一個極性相反的區域隔開,也就是所謂的基極(或稱基體)區域。如果是NMOS,那麼其基體區的摻雜就是p-type。反之對PMOS而言,基體應該是n-type,而源極與汲極則為p-type(而且是重摻雜的P+)。基體的摻雜濃度不需要如源極或汲極那麼高,故在左圖中沒有「+」,作為通道用。

對這個NMOS而言,真正用來作為通道、讓載子通過的只有MOS電容正下方半導體的表面區域。當一個正電壓施加在閘極上,帶負電的電子就會被吸引至表面,形成通道,讓n-type半導體的多數載子—電子可以從源極流向汲極。如果這個電壓被移除,或是放上一個負電壓,那麼通道就無法形成,載子也無法在源極與汲極之間流動,也就是可以透過閘極的電壓控制通道的開關。

假設操作的對象換成PMOS,那麼源極與汲極為p-type、基體則是n-type。在PMOS的閘極上施加負電壓,則半導體上的空穴會被吸引到表面形成通道,半導體的多數載子—空穴則可以從源極流向汲極。假設這個負電壓被移除,或是加上正電壓,那麼通道無法形成,一樣無法讓載子在源極和汲極間流動。

特別要說明的是,源極在金氧半場效電晶體裡的意思是「提供多數載子的來源」。對NMOS而言,多數載子是電子;對PMOS而言,多數載子是空穴。相對的,汲極就是接受多數載子的端點。

金氧半場效電晶體的操作模式

[编辑]

依照在金氧半場效電晶體的閘極、源極,與汲極等三個端點施加的偏置(bias)不同,金氧半場效電晶體將有下列三種操作模式。下面将以一种简化代数模型来讨论。[1]现代MOS管的特性比这里展示的代数模型更加复杂。[2]

对于增强型N沟道MOS管来说,这3种工作模式分别为:

- 截止區(次臨界區或弱反轉區)(cutoff, subthreshold or weak-inversion mode)

- 當 |VGS| < |Vth| 时:

- |VGS| 代表閘極到源極的偏壓差,|Vth| 为材料的臨界電壓。這個金氧半場效電晶體是處在截止(cut-off)的狀態,通道無法反轉,並沒有足夠的多數載子,電流無法流過這個金氧半場效電晶體,也就是這個金氧半場效電晶體不導通。

- 但事實上,金氧半場效電晶體無電流通過的敘述和現實有些微小的差異。在真實的狀況下,因為載子的能量依循麦克斯韦-玻尔兹曼分布而有高低的差異。雖然金氧半場效電晶體的通道沒有形成,但仍然有些具有較高能量的載子可以從半導體表面流至汲極。而若是 |VGS| 略大於零,但小於 |Vth| 的情況下,還會有一個稱為弱反轉層(weak inversion layer)的區域在半導體表面出現,讓更多載子流過。透過弱反轉而從源極流至汲極的載子數量與 |VGS| 的大小之間呈指數的關係,此電流又稱為亚阈值电流(subthreshold current)。

- 在一些擁有大量金氧半場效電晶體的積體電路產品,如动态随机存取存储器(DRAM),次臨界電流往往會造成額外的能量或功率消耗。

- 線性區(三極區或歐姆區)(linear region, triode mode or ohmic mode)[3][4]))

- 當 VGS > Vth 且 VGD > Vth 时:

- 此處VDS為NMOS汲極至源極的電壓,則這顆NMOS為導通的狀況,在氧化層下方的通道也已形成。此時這顆NMOS的行為類似一個壓控電阻(voltage-controlled resistor),而由汲極向源极流出的電流大小為:

- μn是載子遷移率(carrier mobility)、W是金氧半場效電晶體的閘極寬度、L是金氧半場效電晶體的閘極長度,而Cox則是閘極氧化層的單位電容大小。在這個區域內,金氧半場效電晶體的電流—電壓關係有如一個線性方程式,因而稱為線性區。

- 飽和區(主動區)(saturation or active mode)[5][6]

- 當 VGS > Vth 且 VGD < Vth 时:

- 這顆金氧半場效電晶體為導通的狀況,也形成了通道讓電流通過。但是隨著汲極電壓增加,超過閘極電壓時,會使得接近汲極區的反轉層電荷為零,此處的通道消失(如圖),這種狀況稱之為夾止(pinch-off)。在這種狀況下,由源極出發的載子經由通道到達夾止點時,會被注入汲極周圍的空間電荷區(space charge region),再被電場掃入汲極。此時通過金氧半場效電晶體的電流與其汲極—源極間的電壓VDS無關,只與閘極電壓有關,主要原因在於靠近汲極區的閘極電壓已經不足以讓通道反轉,而造成所能提供的載子有限,限制住了通道的電流大小,關係式如下:

- 上述的公式也是理想狀況下,金氧半場效電晶體在飽和區操作的電流與電壓關係式。事實上在飽和區的金氧半場效電晶體汲極電流會因為通道長度調變效應而改變,並非與VDS全然無關。考慮通道長度調變效應之後的飽和區電流—電壓關係式如下:

- 關於通道長度調變效應的成因與影響將在後面敘述。

基板效應

[编辑]一般而言,源極電壓與基板電壓兩者接在一起VSB=0,但在實際上VSB>0(對P型基板而言),此時基板與源極產生逆偏,使得空乏區電荷增加,因此使臨界電壓增加的現象稱為基板效應(Body Effect)。基板效應通常是負面的,臨界電壓之變化常會使類比電路或數位電路設計更加複雜。MOS受到基板效應影響,臨界電壓會有所改變,公式如下:

,

是基極與源極之間無電位差時的臨界電壓,是基板效應參數,則是與半導體能階相關的參數(禁带中线与费米能级的差值)。

金氧半場效電晶體在電子電路上應用的優勢

[编辑]金氧半場效電晶體在1960年由貝爾實驗室的D. Kahng和Martin Atalla首次實作成功,這種元件的操作原理和1947年蕭克利等人發明的雙載子接面電晶體截然不同,且因為製造成本低廉與使用面積較小、高整合度的優勢,在大型積體電路或是超大型積體電路的領域裡,重要性遠超過BJT。

近年來由於金氧半場效電晶體元件的性能逐漸提升,除了傳統上應用於諸如微處理器、微控制器等數位訊號處理的場合上,也有越來越多類比訊號處理的積體電路可以用金氧半場效電晶體來實現,以下分別介紹這些應用。

數位電路

[编辑]數位科技的進步,如微處理器運算效能不斷提升,帶給深入研發新一代金氧半場效電晶體更多的動力,這也使得金氧半場效電晶體本身的操作速度越來越快,幾乎成為各種半導體主動元件中最快的一種。金氧半場效電晶體在數位訊號處理上最主要的成功來自互補式金屬氧化物半導體邏輯電路的發明,這種結構最大的好處是理論上不會有靜態的功率損耗,只有在邏輯閘的切換動作時才有電流通過。互補式金屬氧化物半導體邏輯閘最基本的成員是互補式金屬氧化物半導體反相器,而所有互補式金屬氧化物半導體邏輯閘的基本操作都如同反相器一樣,同一時間內必定只有一種電晶體(NMOS或是PMOS)處在導通的狀態下,另一種必定是截止狀態,這使得從電源端到接地端不會有直接導通的路徑,大量節省了電流或功率的消耗,也降低了積體電路的發熱量。

金氧半場效電晶體在數位電路上應用的另外一大優勢是對直流訊號而言,金氧半場效電晶體的閘極端阻抗為無限大(等效於開路),也就是理論上不會有電流從金氧半場效電晶體的閘極端流向電路裡的接地點,而是完全由電壓控制閘極的形式。這讓金氧半場效電晶體和他們最主要的競爭對手BJT相較之下更為省電,而且也更易於驅動。在CMOS邏輯電路裡,除了負責驅動晶片外負載(off-chip load)的驅動器外,每一級的邏輯閘都只要面對同樣是金氧半場效電晶體的閘極,如此一來較不需考慮邏輯閘本身的驅動力。相較之下,BJT的邏輯電路(例如最常見的TTL)就沒有這些優勢。金氧半場效電晶體的閘極輸入電阻無限大對於電路設計工程師而言亦有其他優點,例如較不需考慮邏輯閘輸出端的負載效應(loading effect)。

類比電路

[编辑]有一段時間,金氧半場效電晶體並非類比電路設計工程師的首選,因為類比電路設計重視的性能參數,如電晶體的跨导或是電流的驅動力上,金氧半場效電晶體不如BJT來得適合類比電路的需求。但是隨著金氧半場效電晶體技術的不斷演進,今日的CMOS技術也已經可以符合很多類比電路的規格需求。再加上金氧半場效電晶體因為結構的關係,沒有BJT的一些致命缺點,如熱跑脫(thermal runaway)。另外,金氧半場效電晶體在線性區的壓控電阻特性亦可在積體電路裡用來取代傳統的多晶矽電阻(poly resistor),或是MOS電容本身可以用來取代常用的多晶矽—絕緣體—多晶矽電容(PIP capacitor),甚至在適當的電路控制下可以表現出電感(inductor)的特性,這些好處都是BJT很難提供的。也就是說,金氧半場效電晶體除了扮演原本電晶體的角色外,也可以用來作為類比電路中大量使用的被動元件(passive device)。這樣的優點讓採用金氧半場效電晶體實現類比電路不但可以滿足規格上的需求,還可以有效縮小晶片的面積,降低生產成本。

隨著半導體製造技術的進步,對於整合更多功能至單一晶片的需求也跟著大幅提升,此時用金氧半場效電晶體設計類比電路的另外一個優點也隨之浮現。為了減少在印刷電路板上使用的積體電路數量、減少封裝成本與縮小系統的體積,很多原本獨立的類比晶片與數位晶片被整合至同一個晶片內。金氧半場效電晶體原本在數位積體電路上就有很大的競爭優勢,在類比積體電路上也大量採用金氧半場效電晶體之後,把這兩種不同功能的電路整合起來的困難度也顯著的下降。另外像是某些混合訊號電路(Mixed-signal circuits),如類比數位轉換器,也得以利用金氧半場效電晶體技術設計出效能更好的產品。

近年來還有一種整合金氧半場效電晶體與BJT各自優點的製程技術:BiCMOS也越來越受歡迎。BJT元件在驅動大電流的能力上仍然比一般的CMOS優異,在可靠度方面也有一些優勢,例如不容易被靜電放電破壞。所以很多同時需要複雜訊號處理以及強大電流驅動能力的積體電路產品會使用BiCMOS技術來製作。

金氧半場效電晶體的尺寸縮放

[编辑]過去數十年來,金氧半場效電晶體的尺寸不斷地變小。早期的積體電路金氧半場效電晶體製程裡,通道長度約在幾個微米的等級。但是到了今日的積體電路製程,這個參數已經縮小到了幾十分之一甚至一百分之一。2008年初,Intel開始以45奈米的技術來製造新一代的微處理器,實際的元件通道長度可能比這個數字還小一些。至90年代末,金氧半場效電晶體尺寸不斷縮小,讓積體電路的效能大大提升,而從歷史的角度來看,這些技術上的突破和半導體製程的進步有著密不可分的關係。

金氧半場效電晶體的尺寸縮小

[编辑]基於以下幾個理由,金氧半場效電晶體的尺寸能越小越好。

- 越小的金氧半場效電晶體象徵其通道長度減少,讓通道的等效電阻也減少,可以讓更多電流通過。雖然通道寬度也可能跟著變小而讓通道等效電阻變大,但是如果能降低單位電阻的大小,那麼這個問題就可以解決。

- 金氧半場效電晶體的尺寸變小意味著閘極面積減少,如此可以降低等效的閘極電容。此外,越小的閘極通常會有更薄的閘極氧化層,這可以讓前面提到的通道單位電阻值降低。不過這樣的改變同時會讓閘極電容反而變得較大,但是和減少的通道電阻相比,獲得的好處仍然多過壞處,而金氧半場效電晶體在尺寸縮小後的切換速度也會因為上面兩個因素加總而變快。

- 金氧半場效電晶體的面積越小,製造晶片的成本就可以降低,在同樣的封裝裡可以裝下更高密度的晶片。一片積體電路製程使用的晶圓尺寸是固定的,所以如果晶片面積越小,同樣大小的晶圓就可以產出更多的晶片,於是成本就變得更低了。

尺寸縮小的負面效應

[编辑]雖然金氧半場效電晶體尺寸縮小可以帶來很多好處,但同時也有很多負面效應伴隨而來。

- 金氧半場效電晶體的尺寸縮小後出現的困難

把金氧半場效電晶體的尺寸縮小到一微米以下對於半導體製程而言是個挑戰,不過現在的新挑戰多半來自尺寸越來越小的金氧半場效電晶體元件所帶來過去不曾出現的物理效應。

- 次臨限傳導

由於金氧半場效電晶體閘極氧化層的厚度也不斷減少,所以閘極電壓的上限也隨之變少,以免過大的電壓造成閘極氧化層突崩潰(breakdown)。為了維持同樣的性能,金氧半場效電晶體的臨界電壓也必須降低,但是這也造成了金氧半場效電晶體越來越難以完全關閉。也就是說,足以造成金氧半場效電晶體通道區發生弱反轉的閘極電壓會比從前更低,於是所謂的亞閾值電流(subthreshold current)造成的問題會比過去更嚴重,特別是今日的積體電路晶片所含有的電晶體數量劇增,在某些超大型積體電路的晶片,次臨限傳導造成的功率消耗竟然佔了總功率消耗的一半以上。

不過反過來說,也有些電路設計會因為金氧半場效電晶體的次臨限傳導得到好處,例如需要較高的轉導/電流轉換比(transconductance-to-current ratio)的電路裡,利用次臨限傳導的金氧半場效電晶體來達成目的的設計也頗為常見。

- 晶片內部連接導線的寄生電容效應

傳統上,互補式金屬氧化物半導體邏輯閘的切換速度與其元件的閘極電容有關。但是當閘極電容隨著金氧半場效電晶體尺寸變小而減少,同樣大小的晶片上可容納更多電晶體時,連接這些電晶體的金屬導線間產生的寄生電容效應就開始主宰邏輯閘的切換速度。如何減少這些寄生電容,成了晶片效率能否向上突破的關鍵之一。

- 晶片發熱量增加

當晶片上的電晶體數量大幅增加後,有一個無法避免的問題也跟著發生了,那就是晶片的發熱量也大幅增加。一般的積體電路元件在高溫下操作可能會導致切換速度受到影響,或是導致可靠度與壽命的問題。在一些發熱量非常高的積體電路晶片如微處理器,目前需要使用外加的散熱系統來緩和這個問題。

在功率電晶體(Power金氧半場效電晶體)的領域裡,通道電阻常常會因為溫度升高而跟著增加,這樣也使得在元件中PN结(pn-junction)導致的功率損耗增加。假設外置的散熱系統無法讓功率電晶體的溫度保持在夠低的水準,很有可能讓這些功率電晶體遭到熱失控的命運。

- 閘極氧化層漏電流增加

閘極氧化層隨著金氧半場效電晶體尺寸變小而越來越薄,目前主流的半導體製程中,甚至已經做出厚度僅有1.2奈米的閘極氧化層,大約等於5個原子疊在一起的厚度而已。在這種尺度下,所有的物理現象都在量子力學所規範的世界內,例如電子的穿隧效應。因為穿隧效應,有些電子有機會越過氧化層所形成的位能障壁(potential barrier)而產生漏電流,這也是今日積體電路晶片功耗的來源之一。

為了解決這個問題,有一些介電係數比二氧化矽更高的物質被用在閘極氧化層中。例如鉿和鋯的金屬氧化物(二氧化鉿、二氧化鋯)等高介電係數的物質均能有效降低閘極漏電流。閘極氧化層的介電係數增加後,閘極的厚度便能增加而維持一樣的電容大小。而較厚的閘極氧化層又可以降低電子透過穿隧效應穿過氧化層的機率,進而降低漏電流。不過利用新材料製作的閘極氧化層也必須考慮其位能障壁的高度,因為這些新材料的傳導帶和價帶和半導體的傳導帶與價帶的差距比二氧化矽小(二氧化矽的傳導帶和矽之間的高度差約為8ev),所以仍然有可能導致閘極漏電流出現。

- 製程變異更難掌控

現代的半導體製程工序複雜而繁多,任何一道製程都有可能造成積體電路晶片上的元件產生些微變異。當金氧半場效電晶體等元件越做越小,這些變異所佔的比例就可能大幅提升,進而影響電路設計者所預期的效能,這樣的變異讓電路設計者的工作變得更為困難。

金氧半場效電晶體的閘極材料

[编辑]理論上金氧半場效電晶體的閘極應該儘可能選擇電性良好的導體,多晶矽在經過重摻雜之後的導電性可以用在金氧半場效電晶體的閘極上,但是並非完美的選擇。目前金氧半場效電晶體使用多晶矽作為的理由如下:

- 金氧半場效電晶體的臨界電壓(threshold voltage)主要由閘極與通道材料的功函數之間的差異來決定,而因為多晶矽本質上是半導體,所以可以藉由摻雜不同極性的雜質來改變其功函數。更重要的是,因為多晶矽和底下作為通道的矽之間能隙相同,因此在降低PMOS或是NMOS的臨界電壓時可以藉由直接調整多晶矽的功函數來達成需求。反過來說,金屬材料的功函數並不像半導體那麼易於改變,如此一來要降低金氧半場效電晶體的臨界電壓就變得比較困難。而且如果想要同時降低PMOS和NMOS的臨界電壓,將需要兩種不同的金屬分別做其閘極材料,對於製程又是一個很大的變數。

- 矽—二氧化矽接面經過多年的研究,已經證實這兩種材料之間的缺陷(defect)是相對而言比較少的。反之,金屬—絕緣體接面的缺陷多,容易在兩者之間形成很多表面能階,大為影響元件的特性。

- 多晶矽的熔點比大多數的金屬高,而在現代的半導體製程中習慣在高溫下沉積閘極材料以增進元件效能。金屬的熔點低,將會影響製程所能使用的溫度上限。

不過多晶矽雖然在過去20年是製造金氧半場效電晶體閘極的標準,但也有若干缺點使得未來仍然有部份金氧半場效電晶體可能使用金屬閘極,這些缺點如下:

- 多晶矽導電性不如金屬,限制了訊號傳遞的速度。雖然可以利用摻雜的方式改善其導電性,但成效仍然有限。目前有些融點比較高的金屬材料如:鎢、鈦、鈷或是鎳被用來和多晶矽製成合金。這類混合材料通常稱為金屬矽化物。加上了金屬矽化物的多晶矽閘極有著比較好的導電特性,而且又能夠耐受高溫製程。此外因為金屬矽化物的位置是在閘極表面,離通道區較遠,所以也不會對金氧半場效電晶體的臨界電壓造成太大影響。

- 在閘極、源極與汲極都鍍上金屬矽化物的製程稱為自我對準金屬矽化物製程(Self-Aligned Silicide),通常簡稱salicide製程。

- 當金氧半場效電晶體的尺寸縮的非常小、閘極氧化層也變得非常薄時,例如現在的製程可以把氧化層縮到一奈米左右的厚度,一種過去沒有發現的現象也隨之產生,這種現象稱為多晶矽空乏。當金氧半場效電晶體的反轉層形成時,有多晶矽空乏現象的金氧半場效電晶體閘極多晶矽靠近氧化層處,會出現一個空乏層(depletion layer),影響金氧半場效電晶體導通的特性。要解決這種問題,金屬閘極是最好的方案。目前可行的材料包括鉭、鎢、氮化鉭(Tantalum Nitride),或是氮化鈦(Titanium Nitride)。這些金屬閘極通常和高介電係數物質形成的氧化層一起構成MOS電容。另外一種解決方案是將多晶矽完全的合金化,稱為FUSI(FUlly-SIlicide polysilicon gate)製程。

各種常見的金氧半場效電晶體技術

[编辑]雙閘極金氧半場效電晶體

[编辑]雙閘極(dual-gate)金氧半場效電晶體通常用在射頻積體電路中,這種金氧半場效電晶體的兩個閘極都可以控制電流大小。在射頻電路的應用上,雙閘極金氧半場效電晶體的第二個閘極大多數用來做增益、混頻器或是頻率轉換的控制。

空乏式MOSFETS

[编辑]一般而言,空乏式(depletion mode)金氧半場效電晶體比前述的加強式(enhancement mode)金氧半場效電晶體少見。空乏式金氧半場效電晶體在製造過程中改變摻雜到通道的雜質濃度,使得這種金氧半場效電晶體的閘極就算沒有加電壓,通道仍然存在。如果想要關閉通道,則必須在閘極施加負電壓(對NMOS而言)。空乏式金氧半場效電晶體是屬於「常閉型」(normally-closed,ON)的開關,而相對的,加強式金氧半場效電晶體則屬於「常斷型」(normally-open,OFF)的開關。

NMOS邏輯

[编辑]同樣驅動能力的NMOS通常比PMOS所佔用的面積小,因此如果只在邏輯閘的設計上使用NMOS的話也能縮小晶片面積。不過NMOS邏輯雖然佔的面積小,卻無法像CMOS邏輯一樣做到不消耗靜態功率,因此在1980年代中期後已經漸漸退出市場,目前以CMOS為主流。

功率金氧半場效電晶體

[编辑]

功率金氧半場效電晶體(Power MOSFET)和前述的金氧半場效電晶體元件在結構上就有著顯著的差異。一般積體電路裡的金氧半場效電晶體都是平面式(planar)的結構,電晶體內的各端點都離晶片表面只有幾個微米的距離。而所有的功率元件都是垂直式(vertical)的結構,讓元件可以同時承受高電壓與高電流的工作環境。一個功率金氧半場效電晶體能耐受的電壓是雜質摻雜濃度與n-type磊晶層(epitaxial layer)厚度的函數,而能通過的電流則和元件的通道寬度有關,通道越寬則能容納越多電流。對於一個平面結構的金氧半場效電晶體而言,能承受的電流以及崩潰電壓的多寡都和其通道的長寬大小有關。對垂直結構的金氧半場效電晶體來說,元件的面積和其能容納的電流大約成正比,磊晶層厚度則和其崩潰電壓成正比。

值得一提的是採用平面式結構的功率金氧半場效電晶體也並非不存在,這類元件主要用在高級的音響放大器中。平面式的功率金氧半場效電晶體在飽和區的特性比垂直結構的對手更好。垂直式功率金氧半場效電晶體則多半用來做開關切換之用,取其導通電阻(turn-on resistance)非常小的優點。

DMOS

[编辑]DMOS是雙重擴散金氧半場效電晶體(Double-Diffused金氧半場效電晶體)的縮寫,大部分的功率金氧半場效電晶體都是採用這種製作方式完成的。

以金氧半場效電晶體實現類比開關

[编辑]金氧半場效電晶體在導通時的通道電阻低,而截止時的電阻近乎無限大,所以適合作為類比訊號的開關(訊號的能量不會因為開關的電阻而損失太多)。金氧半場效電晶體作為開關時,其源極與汲極的分別和其他的應用是不太相同的,因為訊號可以從金氧半場效電晶體閘極以外的任一端進出。對NMOS開關而言,電壓最負的一端就是源極,PMOS則正好相反,電壓最正的一端是源極。金氧半場效電晶體開關能傳輸的訊號會受到其閘極—源極、閘極—汲極,以及汲極到源極的電壓限制,如果超過了電壓的上限可能會導致金氧半場效電晶體燒毀。

金氧半場效電晶體開關的應用範圍很廣,舉凡需要用到取樣保持電路(sample-and-hold circuits)或是截波電路(chopper circuits)的設計,例如類比數位轉換器(A/D converter)或是切換電容濾波器(switch-capacitor filter)上都可以見到金氧半場效電晶體開關的蹤影。

單一金氧半場效電晶體開關

[编辑]當NMOS用來做開關時,其源極接地,閘極為控制開關的端點。當閘極電壓減去源極電壓超過其導通的臨界電壓時,此開關的狀態為導通。閘極電壓繼續升高,則NMOS能通過的電流就更大。NMOS做開關時操作在線性區,因為源極與汲極的電壓在開關為導通時會趨向一致。

PMOS做開關時,其源極接至電路裡電位最高的地方,通常是電源。閘極的電壓比源極低、超過其臨界電壓時,PMOS開關會打開。

NMOS開關能容許通過的電壓上限為(Vgate-Vthn),而PMOS開關則為(Vgate+Vthp),這個值通常不是訊號原本的電壓振幅,也就是說單一金氧半場效電晶體開關會有讓訊號振幅變小、訊號失真的缺點。

雙重(互補式)金氧半場效電晶體(CMOS, Complementary MOS)開關

[编辑]為了改善前述單一金氧半場效電晶體開關造成訊號失真的缺點,於是使用一個PMOS加上一個NMOS的CMOS開關(Transmission gate)成為目前最普遍的做法。CMOS開關將PMOS與NMOS的源極與汲極分別連接在一起,而基極的接法則和NMOS與PMOS的傳統接法相同(PMOS的基極接到最高電壓,即VDD;NMOS的基極接到最低電壓,即VSS或GND)。要令開關導通時,則把PMOS的閘極接低電位(VSS或GND),NMOS的閘極接高電位(VDD)。當輸入電壓在(VDD-Vthn)到(VSS+Vthp)時,PMOS與NMOS都導通,而輸入小於(VSS+Vthp)時,只有NMOS導通,輸入大於(VDD-Vthn)時只有PMOS導通,這樣做的好處是在大部分的輸入電壓下,PMOS與NMOS皆同時導通,如果任一邊的導通電阻上升,則另一邊的導通電阻就會下降,所以開關的電阻幾乎可以保持定值,減少訊號失真。

應用

[编辑]参考文献

[编辑]引用

[编辑]- ^ This model was introduced by H Shichman and DA Hodges. Modeling and simulation of insulated-gate field-effect transistor switching circuits. IEEE Journal of Solid-state circuits. 1968, SC–3: 285–289 [2014-12-23]. doi:10.1109/JSSC.1968.1049902. (原始内容存档于2013-06-10). and often is called the Shichman-Hodges model.

- ^ For example, see Yuhua Cheng, Chenming Hu. MOSFET modeling & BSIM3 user's guide. Springer. 1999. ISBN 0-7923-8575-6.. The most recent version of the BSIM model is described in Sriramkumar V., Navid Paydavosi,Darsen Lu, Chung-Hsun Lin,Mohan Dunga, Shijing Yao, Tanvir Morshed,Ali Niknejad, and Chenming Hu. BSIM-CMG 106.1.0beta Multi-Gate MOSFET Compact Model (PDF). Department of EE and CS, UC Berkeley. 2012 [2012-04-01]. (原始内容 (PDF)存档于2014-07-27).

- ^ C Galup-Montoro & Schneider MC. MOSFET modeling for circuit analysis and design. London/Singapore: World Scientific. 2007: 83 [2014-12-23]. ISBN 981-256-810-7. (原始内容存档于2010-01-12).

- ^ Norbert R Malik. Electronic circuits: analysis, simulation, and design. Englewood Cliffs, NJ: Prentice Hall. 1995: 315–316 [2014-12-23]. ISBN 0-02-374910-5. (原始内容存档于2009-04-27).

- ^ PR Gray, PJ Hurst, SH Lewis & RG Meyer. §1.5.2 p. 45. [2014-12-23]. ISBN 0-471-32168-0. (原始内容存档于2009-04-28).

- ^ A. S. Sedra and K.C. Smith. Microelectronic circuits Fifth Edition. New York: Oxford. 2004: 552 [2014-12-23]. ISBN 0-19-514251-9. (原始内容存档于2009-02-04).

来源

[编辑]- Sze, S. M.,Physics of Semiconductor Devices 2nd ed. New York: Wiley, 1981.

- Donald A. Neamen, Semiconductor Physics & Devices, 3rd ed. McGraw Hill, 2003.

- Behzad Razavi, Design of Analog CMOS Integrated Circuits, 1st ed. McGraw Hill, 2002.

- B. Jayant Baliga, Power Semiconductor Devices, PWS publishing Company, Boston. ISBN 978-0-534-94098-0.

- Adel. S. Sedra and Kenneth. C. Smith, Microelectronics Circuits, 5th ed., Oxford, 2003.

- 施敏; 伍國珏; 譯者:張鼎張、劉柏村. 半導體元件物理學(上冊). 臺灣: 國立交通大學. 2008-08-01 [2008]. ISBN 978-986-843-951-1 (中文). (繁體中文)

- 施敏; 伍國珏; 譯者:張鼎張、劉柏村. 半導體元件物理學(下冊). 臺灣: 國立交通大學. 2009-04-14 [2009]. ISBN 978-986-843-954-2 (中文). (繁體中文)

外部連結

[编辑]- Lessons In Electric Circuits—INSULATED-GATE FIELD-EFFECT TRANSISTORS (页面存档备份,存于互联网档案馆)

- MOSFET models (页面存档备份,存于互联网档案馆) Diagrams and mathematical derivation.

- MIT Open Courseware 6.012 -- 麻省理工學院開放式課程計畫(微電子學與MOSFET元件)

- MIT Open Courseware 6.002 – Spring 2007. [2020-06-11]. (原始内容存档于2010-05-05).

- MIT Open Courseware 6.012 – Fall 2009. [2020-06-11]. (原始内容存档于2012-06-07).

- Georgia Tech BJT and FET Slides. [2020-06-11]. (原始内容存档于2012-03-09).

- CircuitDesign: MOS Diffusion Parasitics. [2020-06-11]. (原始内容存档于2012-08-18).

- Mark Lundstrom, Mark Lundstrom. Course on Physics of Nanoscale Transistors. 2008 [2010-05-09]. (原始内容存档于2012-02-24).

- Dr. Lundstrom. Notes on Ballistic MOSFETs. 2005 [2010-05-18]. (原始内容存档于2012-02-24).