快速通道互联

快速通道互联[1][2](英語:Intel QuickPath Interconnect,縮寫:QPI)[3][4],是一種由英特爾開發並使用的點對點處理器互聯架構,用來實現CPU之間的互聯。英特爾在2008年開始用QPI取代以往用於至強、安騰處理器的前端匯流排(FSB)。初期,英特爾給這種連接架構的名稱是「公共系统界面」(Common System Interface ,CSI)[5][6],它的早期設計形態亦被稱為Yet Another Protocol(YAP)和YAP+。

英特爾在發布Sandy Bridge-EP核心(Romley平台)後,也順勢公佈首代QPI的改進版QPI 1.1版本。[7]Intel於2017年發佈的SkyLake-SP Xeon中,用UPI(UltraPath Interconnect)取代QPI。

背景

[编辑]儘管多數時候被稱作「匯流排」,但是QPI是一種點對點互聯結構。它被設計成與超微半導體自2003年使用的超傳輸(HyperTransport)匯流排競爭。[8][9] 英特爾在它下屬的麻省微處理器研究中心(Massachusetts Microprocessor Design Center,MMDC)開發設計QPI,由以前曾在DEC Alpha的開發團隊的成員進行。這個原先來自DEC的開發團隊此前曾在康柏電腦和惠普工作,後來被英特爾挖角。而關於QPI的研究早在2004年就開始了。[10]

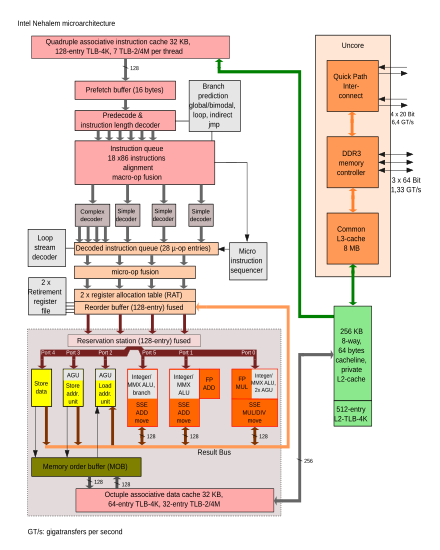

QPI的首次實作是英特爾自家的Nehalem微架構。在2008年11月發售的桌上型平台處理器Core i7-900系列和X58晶片組上、在2009年3月發布伺服器平台的Xeon X5500系列處理器。後來,2010年2月發布的Itanium 2處理器(核心代號「Tukwila」),也使用了QPI。[11]

實作

[编辑]

QPI通常作為一個系統架構的組成部分,英特爾稱之為「快速通道架构」(QuickPath architecture),這個架構的實作英特爾又稱之為「快速通道技术」(QuickPath technology)。[12]在QPI最簡單的佈置形態——單處理器主機板上,QPI可用來將像是北橋晶片、南橋晶片的IO Hub和處理器對等連接,像是早期Core i7-900系列與X58晶片組之間的連接。在一些更複雜的架構的例子中,多個QPI鏈接可將一個以上的處理器或一個以上的IO Hub甚至主機板網路上的路由集線器對等連接起來,允許各個組件通過這個網路來與另一個組件進行通信。和HyperTransport匯流排類似,搭載快速互聯架構的處理器亦需要內建記憶體控制器,支援非均勻存取架構。

每個QPI包括有兩個20連線的點對點資料通道,每個通道一個傳送方向,而每一方向還配備單獨的時鐘信號對(發送TX,接收RX),與資料訊號一起形成共42個信號,如此一來達成全雙工運作。每個時鐘信號採用差動信號的形式傳送,因此QPI的信號線共84條。20條連線被劃分為四等份,每份5條連線。QPI中基本資料傳送單元是80位元大小的QPI資料封包,每兩個時鐘週期完成一次一個QPI資料封包的傳送,在這兩個時鐘週期內,一個QPI資料封包是分為四次傳送,每次傳送20位元,即一個時鐘週期內傳送兩次。每個80位元的QPI資料封包內有8位元用於錯誤糾正,8位元是「鏈路層報頭」,剩下的64位元才是包含的真實有效的資料。QPI的頻寬的計算上,建議計算每兩個時鐘週期每方向傳送的有效資料量,由於QPI是雙向傳送的,因此每方向在兩個時鐘週期內都會有包含64位元(8位元組)有效資料的資料封包的傳送。[13]

儘管最初QPI僅實現四象限鏈接,但QPI的規格容許其它實作。每個象限可以獨立使用。在高可靠度伺服器上,一個QPI鏈接可以在降階模式中運作。如果20+1信號中一個或多個鏈路失效,介面將剩餘的鏈路以10+1或最低5+1信號來繼續運作,如果時鐘失效,甚至會為資料信號重新分配時鐘。[13]

最初實現四象限鏈路的是Nehalem架構的4核心處理器,使用完整的四象限鏈接QPI介面達成25.6GB/s的頻寬,提供兩倍於英特爾自家的X48晶片組上使用的1600MHz FSB的理論頻寬。

儘管最早Core i7-900系列全面使用QPI,但其它Nehalem架構至桌上型處理器和行動型處理器,像是Core i3、Core i5以及其它Core i7系列(Lynnfield核心、Clarksfield核心以及其後續核心型號)的處理器,這些處理器因無需參與到多處理器系統上(從市場取向上也沒有必要加入該特性),因此任何外部存取方式上都沒有使用QPI,儘管這些處理器內部仍然使用QPI,用以連接處理器內的「Uncore」(「Uncore」指的是處理器晶片的一部分,包含記憶體控制器、PCI-E控制器、以及內建GPU,乃至整個北橋),這種設計可見於基於Westmere微架構的Clarkdale核心及Arrandale核心型號上(即首代Core i3、i5)[14][15][16][17][18]:p.3而這些系列的處理器,北橋已經移到處理器內部作為「Uncore」(或稱「片上北橋」)的一部分,和處理器核心直接連接,無需再以前端匯流排界面連接,處理器的外部連結通過片上北橋/Uncore使用較慢的DMI(2.5GT/s至5.0GT/s的吞吐量)或PCI-e匯流排介面,用來連接南橋/PCH或其它形式的外部裝置。[19]Nehalem/Westmere微架構上,Uncore/片上北橋與處理器核心尚用QPI連接,而Sandy Bridge微架構以後的桌上型平台以及行動平台之處理器上則採用基於QPI衍生的環形匯流排鏈路連接,同時也保證快取一致性。[18]:p.10

時脈規格

[编辑]QPI的運作時脈有2.4GHz、2.93GHz、3.2GHz或4.0GHz(4.0GHz用於企業級的Sandy Bridge-E/EP核心的處理器上)。每個特定鏈路的時脈取決於鏈路終端的組件之性能以及印刷電路板上信號路徑的信號特徵,亦即可根據所連接組件的資料吞吐量需求自行調整時脈,提高資源利用效率。[20]最初,非極致版本的Core i7-900系列的處理器出廠預設的QPI時脈被限定在2.4GHz。由於採用了雙倍資料率技術(DDR),位元的傳送在時鐘脈衝信號的上升沿和下降沿都進行,因此,資料傳送的實際時脈是時鐘時脈的兩倍。

英特爾以80位元的QPI資料封包封裝的64位元實際有效資料的傳送量計數,來描述資料吞吐量和頻寬。然而,由於單向發送和單向接收鏈路對是同步進行的,亦即全雙工作業,英特爾後來將結果數字改為原來的兩倍。因此,英特爾描述中,一個運作於3.2GHz時脈速率的20通道的QPI鏈接對(發送和接收)擁有6.4GT/s的資料傳送速率,25.6GB/s的頻寬,而同樣通道數的QPI運作於2.4GHz時資料傳送速率是4.8GT/s,頻寬19.2GB/s。更通常地,根據這個定義,一個兩端鏈結的20通道QPI每時鐘週期傳送8位元組,每方向4位元組。

頻寬計算:(以運作於3.2GHz時脈速率下,吞吐量6.4GT/s)[21]

- 3.2 GHz

- × 2 bits/Hz (雙倍資料傳送速率)

- × 20 (QPI連接寬度)

- × (64/80) (資料位元數/資料封包位元數)

- × 2 (各向發送和接收作業同步進行)

- ÷ 8 (每位元組位元數)

- = 25.6 GB/s

或:

- 6.4 GT/s

- × 2 Byte (每次傳輸的有效資料,64位元/4次/8位元一個位元組=2位元組每次)

- × 2 (各項發送和接收作業同時進行)

- = 25.6 GB/s

如此類推,2.4GHz或4.8GT/s、4.0GHz或8.0GT/s、2.93GHz或5.86GT/s的也可以計算出頻寬。

協定層

[编辑]QPI的協定定義了五層結構,分為物理層、鏈路層、路由層、傳輸層以及協定層。[3]但是,在一些僅兩節點的點對點QPI配置組態上,像是Core i7-900系列和Xeon雙處理器平台(DP)系列的處理器,不需要傳輸層,路由層是最小最簡單的兩節點組態。

- 物理層:物理層包含實際接線、差分發送器和接收器、加上發送和接收的物理層單元的最低級邏輯。所謂的物理層單元是20位元的封包分塊。當20個通道全部可用時,物理層利用1個單一時鐘信號邊沿在20個通道上傳輸20位元的封包分塊,如果遇到失效/傳輸失敗的情況時,QPI會重新配置,僅使用10個甚至只有5個通道來傳輸封包分塊。注意,除了資料信號以外,會有一個時鐘信號從發送器傳送到接收器上(這需要佔用一個額外的引腳來簡化時鐘恢復過程)。

- 鏈路層:鏈路層負責發送和接收80位元的封包。每個封包發送至物理層上是作為4個20位元的封包分塊的形式。每個封包包括一個8位元的CRC(循環冗餘校驗),由鏈路層發送器生成,72位元是封包所承載的資料。如果鏈路層檢測到一個CRC錯誤,發送器通過一對鏈路中的返回鏈路發回一個封包通知發送器重發封包。為防止接收器的緩衝區溢出,鏈路層還通過賒賬/借記的方案來實現資料流量控制。鏈路層支援六種不同類型的消息,來允許更高的協定層識別封包中主要用於保持快取一致性非資料部分並將之拆分以掠過。在實作一些複雜的快速通道架構上,鏈路層可被配置成為不同類別的資料流保持資料流分離和流量控制。但是,在單處理器和雙處理器平台上實作的快速通道架構,這方面的實作需要仍不明確。

- 路由層:路由層傳送一個包含一個8位元報頭和64位元資料承載的72位元單元。報頭包括資料目的地和消息類型。當路由層接收到一個單元,它會檢查它的路由表以確定單元是否到達目的地。如果單元已到達目的地的話,就將之傳遞至更高的協定層上。如果仍未到達目的地,單元將被發送到正確的向外傳輸QPI。在只有單一QPI架構的裝置上,路由層是最小的。在更複雜的實作範例上,路由層的路由表會更為複雜、而且被定制成動態更新以避免失效的QPI連結。

- 傳送層:僅有兩節點的連接中,傳送層並不是必須的,而且亦不會出現在這些裝置上,像是Core i7。傳送層可跨越QPI網路發送和接收資料,這個QPI網路由其它多個裝置上的數個節點以QPI連接組成,這些裝置也可能並沒有直接連接(舉個例子,資料可能會由一個已被插斷的裝置上經過),傳送層會校驗資料的完整性,如果資料不完整,它會要求上一個節點重新發送資料。

- 協定層:協定層發送和接收代表裝置的封包。一個典型的封包是一個記憶體快取行。協定層也通過發送和接收快取一致性消息的方式參與到快取一致性的維持。

參見

[编辑]資料來源

[编辑]- ^ 英特爾. 英特尔® 快速通道互联简介. 英特爾. [2013-10-10]. (原始内容存档于2020-10-22).

- ^ 英特爾. 英特尔® 快速通道互联架构. 英特爾. [2013-10-10]. (原始内容存档于2013-10-17).

- ^ 3.0 3.1 An Introduction to the Intel QuickPath Interconnect (PDF). Intel Corporation. January 30, 2009 [June 14, 2011]. (原始内容存档 (PDF)于2011-04-16).

- ^ DailyTech report (页面存档备份,存于互联网档案馆), retrieved August 21, 2007

- ^ Eva Glass. Intel CSI name revealed: Slow, slow, quick quick slow. The Inquirer. May 16, 2007 [September 13, 2013]. (原始内容存档于2012-06-10).

- ^ QPI总线是什么. pconline.com.cn. [2013-10-10]. (原始内容存档于2019-11-13).

- ^ David Kanter. Intel's Quick Path Evolved. Realworldtech.com. 2011-07-20 [2014-01-21]. (原始内容存档于2021-01-21).

- ^ Gabriel Torres. Everything You Need to Know About The QuickPath Interconnect (QPI). Hardware Secrets. August 25, 2008 [September 13, 2013]. (原始内容存档于2014年10月27日).

- ^ Charlie Demerjian. Intel Intel gets knickers in a twist over Tanglewood. The Inquirer. December 13, 2005 [September 13, 2013]. (原始内容存档于2010-09-03).

- ^ Eva Glass. Intel's Whitefield takes four core IA-32 shape. The Inquirer. December 12, 2004 [September 13, 2013]. (原始内容存档于2009-05-24).

- ^ David Kanter. Intel’s Tukwila Confirmed to be Quad Core. Real World Tech. May 5, 2006 [September 13, 2013]. (原始内容存档于2012年5月10日).

- ^ Intel Demonstrates Industry's First 32nm Chip and Next-Generation Nehalem Microprocessor Architecture. [2007-12-31]. (原始内容存档于2008-01-02).

- ^ 13.0 13.1 David Kanter. The Common System Interface: Intel's Future Interconnect. Real World Tech. August 28, 2007 [September 13, 2013]. (原始内容存档于2007年9月27日).

- ^ 集显U会限制超频么?酷睿i3-530超频实测. zol.com.cn. [2014-08-07]. (原始内容存档于2012-03-20).

- ^ Chris Angelini. QPI, Integrated Memory, PCI Express, And LGA 1156 - Intel Core i5 And Core i7: Intel’s Mainstream Magnum Opus. Tomshardware.com. 2009-09-07 [2014-01-21]. (原始内容存档于2012-02-23).

- ^ Published on 25th January 2010 by Richard Swinburne. Feature - Intel GMA HD Graphics Performance. bit-tech.net. 2010-01-25 [2014-01-21]. (原始内容存档于2017-05-21).

- ^ Intel Clarkdale 32nm CPU-and-GPU chip benchmarked (again) - CPU - Feature. HEXUS.net. 2009-09-25 [2014-01-21]. (原始内容存档于2020-08-08).

- ^ 18.0 18.1 Oded Lempel. 2nd Generation Intel Core Processor Family: Intel Core i7, i5 and i3 (PDF). hotchips.org. 2013-07-28 [2014-01-21]. (原始内容 (PDF)存档于2020-07-29).

- ^ Lily Looi, Stephan Jourdan, Transitioning the Intel® Next Generation Microarchitectures (Nehalem and Westmere) into the Mainstream (页面存档备份,存于互联网档案馆), Hot Chips 21, August 24, 2009

- ^ CPU : 什么是QPI总线 (页面存档备份,存于互联网档案馆)-zol.com.cn

- ^ GT/s MHz?——解密QPI的来龙去脉 (页面存档备份,存于互联网档案馆) - enet.com.cn

外部連結

[编辑]- First Look at Nehalem Microarchitecture

- Ars Technica's What You Need To Know About Nehalem (页面存档备份,存于互联网档案馆)

- An Introduction to the Intel QuickPath Interconnect (页面存档备份,存于互联网档案馆)